- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC24F08KL301-I/SS (Microchip Technology)IC MCU 16BIT 8KB FLASH 20-SSOP

PIC24F16KL402

FAMILY

DS3

1037B-page

39

20

11

M

ic

rochip

T

e

chnology

In

c.

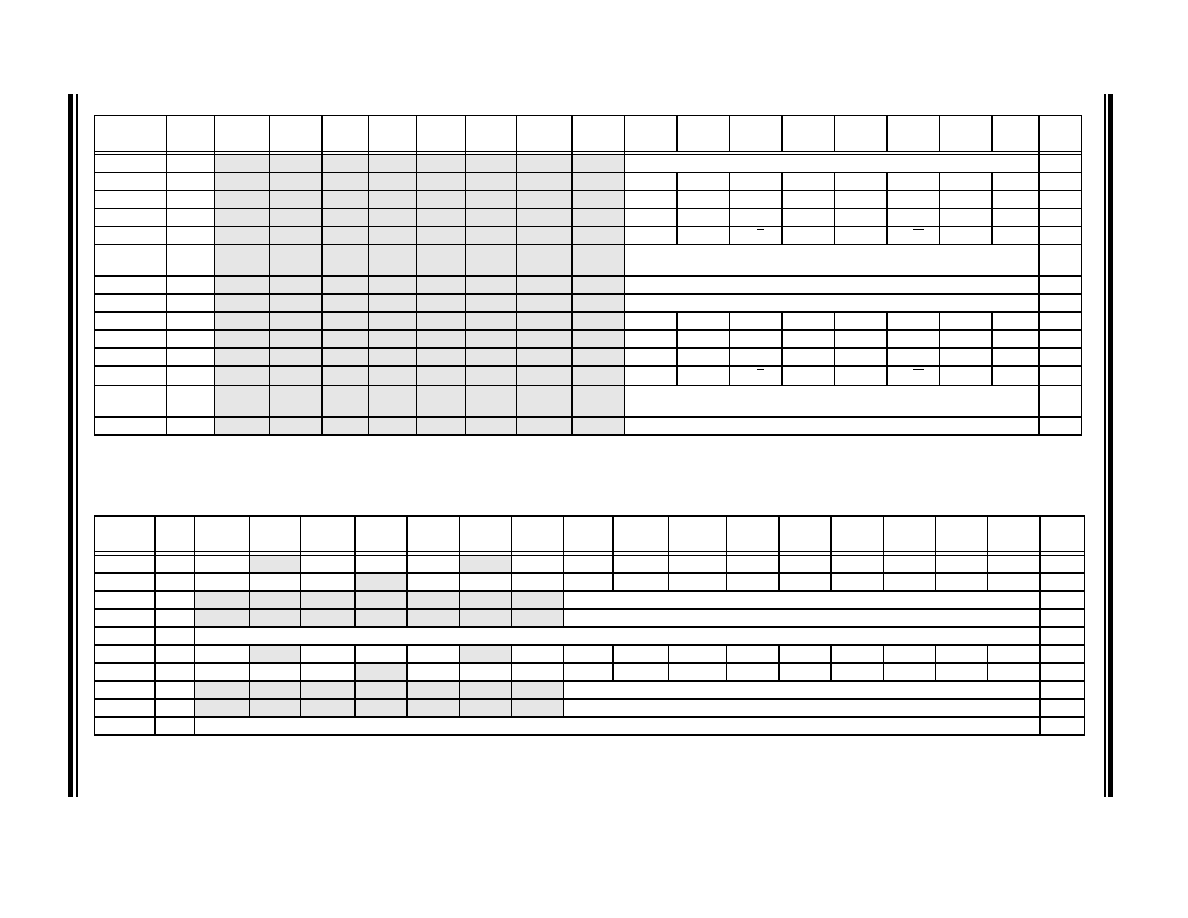

TABLE 4-8:

MSSP REGISTER MAP

File Name

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

SSP1BUF

0200

—

MSSP1 Receive Buffer/Transmit Register

00xx

SSP1CON1

0202

—

WCOL

SSPOV

SSPEN

CKP

SSPM3

SSPM2

SSPM1

SSPM0

0000

SSP1CON2

0204

—

GCEN

ACKSTAT

ACKDT

ACKEN

RCEN

PEN

RSEN

SEN

0000

SSP1CON3

0206

—

ACKTIM

PCIE

SCIE

BOEN

SDAHT

SBCDE

AHEN

DHEN

0000

SSP1STAT

0208

—

—SMP

CKE

D/A

PS

R/W

UA

BF

0000

SSP1ADD

020A

—

MSSP1 Address Register (I2C Slave Mode)

MSSP1 Baud Rate Reload Register (I2C Master Mode)

0000

SSP1MSK

020C

—

MSSP1 Address Mask Register (I2C Slave Mode)

00FF

SSP2BUF(1)

0210

—

MSSP2 Receive Buffer/Transmit Register

00xx

SSP2CON1(1)

0212

—

WCOL

SSPOV

SSPEN

CKP

SSPM3

SSPM2

SSPM1

SSPM0

0000

SSP2CON2(1)

0214

—

GCEN

ACKSTAT

ACKDT

ACKEN

RCEN

PEN

RSEN

SEN

0000

SSP2CON3(1)

0216

—

ACKTIM

PCIE

SCIE

BOEN

SDAHT

SBCDE

AHEN

DHEN

0000

SSP2STAT(1)

0218

—

—SMP

CKE

D/A

PS

R/W

UA

BF

0000

SSP2ADD(1)

021A

—

MSSP2 Address Register (I2C Slave Mode)

MSSP2 Baud Rate Reload Register (I2C Master Mode)

0000

SSP2MSK(1)

021C

—

MSSP2 Address Mask Register (I2C Slave Mode)

00FF

Legend:

— = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

Note 1:

These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as ‘0’.

TABLE 4-9:

UART REGISTER MAP

File

Name

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

U1MODE

0220

UARTEN

—

USIDL

IREN

RTSMD

—

UEN1

UEN0

WAKE

LPBACK

ABAUD

RXINV

BRGH

PDSEL1

PDSEL0

STSEL

0000

U1STA

0222

UTXISEL1 UTXINV UTXISEL0

—

UTXBRK

UTXEN

UTXBF

TRMT

URXISEL1 URXISEL0

ADDEN

RIDLE

PERR

FERR

OERR

URXDA

0110

U1TXREG

0224

—

UART1 Transmit Register

xxxx

U1RXREG

0226

—

UART1 Receive Register

0000

U1BRG

0228

Baud Rate Generator Prescaler Register

0000

U2MODE

0230

UARTEN

—

USIDL

IREN

RTSMD

—

UEN1

UEN0

WAKE

LPBACK

ABAUD

RXINV

BRGH

PDSEL1

PDSEL0

STSEL

0000

U2STA

0232 UTXISEL1 UTXINV UTXISEL0

—

UTXBRK

UTXEN

UTXBF

TRMT

URXISEL1 URXISEL0

ADDEN

RIDLE

PERR

FERR

OERR

URXDA

0110

U2TXREG

0234

—

UART2 Transmit Register

xxxx

U2RXREG

0236

—

UART2 Receive Register

0000

U2BRG

0238

Baud Rate Generator Prescaler Register

0000

Legend:

— = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF1220T-I/ML

IC MCU FLASH 2KX16 EEPROM 28QFN

PIC18LF1220T-I/SO

IC MCU FLASH 2KX16 EEPROM 18SOIC

PIC16F716-I/SS

IC PIC MCU FLASH 2KX14 20SSOP

PIC18F1320T-E/ML

IC MCU FLASH 4KX16 EEPROM 28QFN

PIC16LF87T-I/ML

IC MCU FLASH 4KX14 EEPROM 28QFN

PIC18F25J10-I/SS

IC PIC MCU FLASH 16KX16 28SSOP

PIC16F88T-E/SS

IC MCU FLASH 4KX14 EEPROM 20SSOP

PIC16C621A-04/SO

IC MCU OTP 1KX14 COMP 18SOIC

相关代理商/技术参数

PIC24F08KL301T-I/MQ

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL301T-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL301T-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Low-Power, Low-Cost, General Purpose 16-Bit Flash Microcontrollers with nanoWatt XLP Technology

PIC24F08KL302-I/ML

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/MQ

功能描述:16位微控制器 - MCU 8KB FL 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SP

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT